Definition

Synthesis is the process of converting RTL (Register Transfer Level) code (i.e.., Verilog format) to optimized Gate level netlist to the targeted technology by meeting area, timing and power constraints.

Types of synthesis

There are 2 types of synthesis techniques which are in use to convert RTL code to gatelevel netlist:

1. Logic synthesis

2. Physical aware synthesis

Logic Synthesis

The below flow chart shows the cadence logic synthesis flow to convert RTL code to netlist (almost all tools follow the same flow with minimal changes)

some popular tools for synthesis are:

Genus – Cadence

Design Compiler – Synopsys

Now a days most of the companies are moving to Fusion Compiler (Synosys) instead of Design Compiler. The main advantage of this tool is we can do both synthesis and PnR in the same tool. In other words it is a combination of both Design Compiler & ICC2

Logic synthesis flow

Importing Input files (RTL code and .lib files)

⇩

Elaborate

⇩

Read SDC file

⇩

Sanity checks (check_design, check_timing)

⇩

Generic mapping

⇩

Technology mapping

⇩

Optimization

⇩

DFT (Design For Testability) implementation (Done by DFT team)

⇩

Incremental optimization

⇩

Generating outputs (Netlist, SDC, Scan DEF, Required reports)

Let us see each step of the flow in a detailed way

Inputs of logic synthesis

At first step we will import all required input files to the Genus compiler i.e

- RTL code

- Timing libraries(.lib files)

- SDC (synopsis design constraints)

Elaborate

In this step the tool will elaborate the RTL code which we have given as input during first step. During the elaboration step mainly 3 tasks are performed:

- Data structure: No. of RTL files are given as input to the tool. So, the tool takes all these files and makes a single netlist from all these Verilog files.

- Infers registers: It infers (to make a well informed guess) the decision trees like if..else… statements to mux and latches or flops.

- The synthesis tool infers a flip flop whenever a “posedge” or “negedge” construct is present.

- Tool infers “if…else…” as mux.

- Similarly, case statements are infers as priority encoders.

- HDL optimization: In this step, tool removes dead codes, unloaded outputs, combinational loops, floating inputs, etc..,

Read SDC

Read SDC is a command used to read all the contents of SDC file.SDC means Synopsis Design Constraints. It contains design timing information, wireload models and DRV’S .These constraints are like timing guidelines for the design, tool always follows these constraints.

what is DRV’S: DRV’S stands for Design Rule Violations.Every design should be DRV free.In simple words if we give some limit for the tool to do a task.The tool must do the task in the given limit only.If it fails to perform a task in given limit then DRV’s occurs. DRVs are 4 types:

Max transition, Max Capacitance, Max Fanout, Max Length.

Note: Max transition and Max Capacitance are considered as hard constraints. These two should not violated in the design and mandatory to fix. And Max Fanout and Max length are considered as Soft constraints that means these can be ignored even violate not mandatory to fix.

Sanity checks

Before the mapping stage, we must perfom sanity checks on RTL code and SDC file to check the quality of input files .The various sanity checks are

check_design: It reports design information like combinational loops, unintended latches, floating inputs, dead codes, multidriven nets.

check_timing: It checks SDC file (mandatory check). It reports any issues present in the file. Some of the issues are:

- Missing clock definition

- Unconstrained endpoints

- Missing Input/output delays for the ports

- Clock reaching to all the sequential elements

- Multi clock driven registers

- Missing slew or load constraints for the ports

Note: If we found any issues in input files during sanity checks we do not proceed we will sent back those input files to Frontend team with describing the issue.

Generic mapping

During generic mapping, tool converts RTL code to the symbolic gate level representation. Tool maps the cells to the generic library. It is independent of technology.

Example of generic netlist

Following “flipflop_generic_netlist.v” shows the example generic netlist for a flipflop.

module flop (clk, reset, next_clk_enable, clk_enable);

input clk, reset, next_clk_enable;

output clk_enable;

wire clk, reset, next_clk_enable;

wire clk_enable;

CDN_flop clk_enable_reg_reg(.clk (clk), .d (next_clk_enable), .sena (1'b1), .aclr (1'b0), .apre (reset), .srl (1'b0), .srd (1'b0), .q (clk_enable));

endmodule

`ifdef RC_CDN_GENERIC_GATE

`else

module CDN_flop(clk, d, sena, aclr, apre, srl, srd, q);

input clk, d, sena, aclr, apre, srl, srd;

output q;

wire clk, d, sena, aclr, apre, srl, srd;

wire q;

reg qi;

assign #1 q = qi;

always

@(posedgeclk or posedgeapre or posedgeaclr)

if (aclr)

qi<= 0;

else if (apre)

qi<= 1;

else if (srl)

qi<= srd;

else begin

if (sena)

qi<= d;

end

initial

qi<= 1'b0;

endmodule

`endif

In this step, logic optimization also done by the tool. Logic optimization means tool removes all unwanted wires, cells, flipflops with constant logic ‘0’ or logic ‘1’.

Technology mapping

During this step, tool maps generic gate to the targeted technology gates by using targeted library files. Targeted technology gates will have gate area, timing and power, this info present in the .lib file.

Example of targetted technology netlist

Following “tech_mapped_netlist.v” shows the example targeted technology netlist for flipflop

module flop (clk, reset, next_clk_enable, clk_enable);

input clk, reset, next_clk_enable;

output clk_enable;

wire clk, n_3, next_clk_enable;

wire clk_enable;

DFFSHQX1 clk_enable_reg_reg(.SN (n_3), .CK (clk), .D (next_clk_enable), .Q (clk_enable));

endmodule

Optimization

During optimization, tool optimizes the design to meet all design constraints (area, timing and power). Some of optimization techniques are changing VT of cells, changing drive strength of cells, logic restructuring, adding repeaters, cloning and buffering.

DFT (Design For Testability) implementation

- DFT is one of the most important process in the SOC design cycle, which helps us in detecting manufacturing defects in the designs.

- DFT engineer works on inserting extra hardware blocks as part of the design itself, for increasing the testability of chips.

- Testing is required to guarantee fault-free chips.

- DFT team will insert scan chains to the design.Scan chains are nothing but adding extra input and enable pin to the flops,these are used to check wheather the flop is working or not by giving test inputs during testing

Incremental optimization

After scan insertion, one more round of optimization has to do that is called Incremental optimization.We will use same optimization techniques as discussed above

Generating outputs

Outputs of logic synthesis are:

- Optimized gatelevel netlist

- SDC

- Scan DEF: Info for scan connection between the flops in the design

- Reports

Physical aware synthesis

Physical aware synthesis is bit advance compared to logic synthesis. Because physical aware synthesis not only converts RTL code to gatelevel netlist but also places the standard cells in the core area to meet all requirements like area, power and timing.

Physical aware synthesis flow is also same as logic synthesis. But some add-ons are there in input files and generating output files.

Input files

- RTL code

- Physical libraries and technology (.lef)

- MMMC file

- Timing libraries (.lib)

- SDC file

- Captables or qrcTech file

- Floorplan DEF (optional)

- UPF – Unified Power Format (optional – only if the design have multiple power domains)

During mapping, tool place standard cells in the core area. If the floorplan DEF is not given as input ,the tool estimates core area based on gate area and places the cell in the core area.

Compared to wireload model synthesis, this method is more accurate. If we use physical aware synthesis, the timing findings before and after actual placement would be more closely related to one another.

Outputs of the physical aware synthesis

- Gatelevel netlist

- SDC file

- Scan DEF

- Reports

- Placed DEF file

- MMMC file

Practical approach for Synthesis

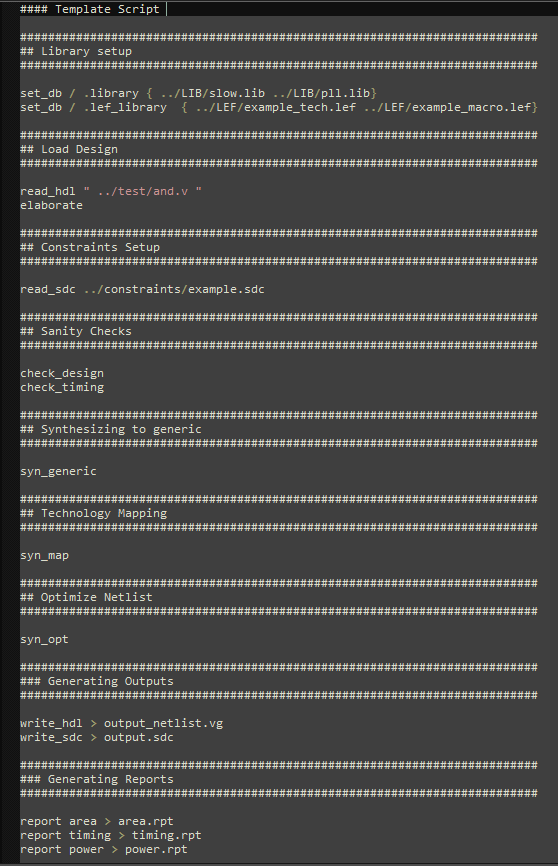

step 1 : Importing input files (RTL code & .Lib Files) → Here in this command ../ means one folder back from the current directory. LIB is the folder name & slow.lib is the file name which we want to use it as library for our design

set_db / .library { ../LIB/slow.lib ../LIB/pll.lib}

set_db / .lef_library { ../LEF/example_tech.lef ../LEF/example_macro.lef ../LEF/pll.lef}

step 2 : Read hdl & Elaborate → The command read_hdl is used to read hdl code (verilog code) here and.v is our input file

read_hdl " ../test/and.v "

elaborate

step 3 :Read SDC file → The command read_sdc is used to read SDC file here example.sdc is our SDC file

read_sdc ../constraints/example.sdc

step 4 : Sanity Checks

check_design

check_timing

step 5 : Generic Mapping → The command syn_generic is used for generic mapping

syn_generic

step 6 :Technology Mapping → The command syn_map is used for technology mapping

syn_map

Note: without generic mapping also we can do directly technology mapping. But the advantage of doing generic mapping is generic mapped file can be mapped with any technology without doing the whole process again.

For instance we run the synthesis, generated the generic mapped file and mapped to 90nm technology but later due to change in requirements we need to map with 65nm technology.In that case we dont need to do whole synthesis again we just use already generated generic map file to map with 65nm technology

step 7 : Optimization → The command syn_opt is used for optimization

syn_opt

step 8 : Generating Outputs → In this step we will generate outputs.Here we are gerenating outputs in the same directory if we want to generate outputs in different directory then we have to give the path where we want the file

For example

write_sdc > /home/test/output.sdc

In this example output.sdc will be genertaed in the test folder

write_hdl > output_netlist.vg

write_sdc > output.sdc

step 9 : Generating Reports → Generating reports are also similar to generating outputs here only thing will change is the commmands used to generate reports

report area > area.rpt

report timing > timing.rpt

report power > power.rpt

Example of Synthesis template

Here the commands used in the script are tool related commands, if we need to excute the entire commands by one click we need to write all commands in one file just shown in the below example and add extension like .tcl or .pl. Tool Command Language (tcl) ,Perl (pl) are nothing but scripting languages most widely using in VLSI industry. Python (.py) also used for some advanced applications.

If you have any doubts regarding the Synthesis feel free to comment below

This site provides useful information for freshers please keep posting more topics on vlsi thank you…

Thanks for your feedback

you are providing a good information for learner as well as experience persons

thank you

Thank you for your comment! We’re thrilled to hear that you found our content valuable.

It was helpful. Thanks for adding important information.

but how does we optimize any violation in timing report and others.

Generally for timing violations in synthesis first we check for constraints are proper or not and use path groups to remove timing violations

Hi vlsitalks

Thanks for the content posted

SDC is input as well as out put

So what are the changes after synthesis

Please explain

Hi Priya,

Usually, there will be no change in SDC file while before and after synthesis (Whatever given as input will be the same at output) But based on timing analysis we keep updating constraints like input output delays ,many exceptions & many more constraints gets added and these all come in updated SDC as output of synthesis

how can we remove timing violations

Can you brief it out…..

Generally we didn’t do much fixes in synthesis stage anyway for timing violations we do pathgroups, cellsizing,Vt swapping etc.

Ok

Thank you

Can u specify the commands.

And when to use which thing.

STA is not opening

We are working on STA and other topic, soon will upload…

Can you please explain the generic mapping and technology mapping?

see, at the generic stage, RTL code is converted into the circuit level. you can find only a schematic (symbolic gates) of the logic written in RTL, but that schematic couldn’t have any physical or timing information. During technology mapping, symbolic gates are mapped to the targeted technology, then timing, area, and power info comes. I hope you understand this…

Don’t we insert clock gates during the synthesis stage?

Clock gating cells have to insert at the synthesis stage only.

can you explain it ..?

1. What are the optimazation techniques( for better timing, area, power) tool will perform exactly during syn_generic, syn_map, syn_opt and post dft stitching?

2. Please confirm that, during elaboration tool will perform data structuring and data optimization on RTL code only?

3. Please explain during physical synthesis, when we read floorplan def on post stitching netlist what operations synthesis tool will perform and please explain optimization techniques performed at this stage?

1) For area: mainly tool goes for logic restructuring.

For timing: pin swapping, Vt swapping, upsizing or downsizing, load splitting, cloning, buffering, and replacing single buffer with inverter pair.

For power: Vt swapping, upsizing, or downsizing

Note: remember one thing if you want to improve power then it may affect timing and area. If you are trying to improve the timing then it may affect the area and power and similarly, if you want to better area then it may affect timing and power.

2) Yes, during elobrarte tool optimzes RTL code.

3) Usually, floorplan DEF is given to the tool before the generic mapping.

Thank you for generous response

1. The optimization techniques you’ve mentioned are happens during which stage like, syn_generic,syn_map, syn_opt or incremental opt?

3. I’ve seen reading def on post_stiching netlist only.

1) During generic, major optimization is logic restructuring, and from technology mapping, all opt techniques are common for all stages tool chooses techniques based on the issues.

2) Actually we can give at any stage and if DEF is not given to the tool then the tool calculates the total cell area and it will create core area and places the cells. if you have tool access do experiment with it.

what is a single buffer and why is it slower than inverter pair ? I often think that an inverter pair as a buffer would have switching losses. So it there a power efficient buffer ?

Inverter pair: improve signal quality, reduce noise, and enhance the driving capability of the circuit.

Buffer: when a signal must be sent over a greater distance or through more than one gate. They help prevent signal degradation due to parasitic and other factors which can weaken the signal as it travels along a trace or through a wire.

amazing content; I greatly appreciate your efforts.

Thank you

Very Good Content. It is very helpful for me.

Great Efforts,

Can you please upload standard cell characterisation and DFT contents.

Thank you so much for you patience and help.

Thanks for your comment we are looking forward to upload Dft contents keep supporting us

During physical aware synthesis, along with conversion of RTL code to netlist, the tool places standard cells in core area => refers to actual placement of standard cells which happens at PNR stage, or the tool just places standard cells at the origin of the core area?

At physical synthesis stage tool places the standard cells and perform timing analysis (TNS, WNS) also placement have to perform in PnR again. The placement happened in the Physical synthesis is not the actual placement.

Hi

Is physical aware synthesis is done in fusion complier right? Where synthesis and PnR done parallely

Hello Mounika,

Yes, Physical aware synthesis can be done in Fusion compiler. The flow is PS and then PnR.

Hi

Is it WLM is used for delay calculation in Physical synthesis using FC?May i know pls.

Thanks

We appreciate your interest in our content. WLM uses in Logic synthesis but coming to Physical synthesis, RC coefficient files are giving as input. so based on the distance cells placed tool calculates the delay which will almost matches the PnR delays. Conclusion, for physical synthesis WLM are no need for delay calculation.

Hi

Thank you very much for your quick reply.

Thank you for your positive response. We are always here to help our followers…

Hi

I have one more doubt regarding physical synthesis performing using FC tool,as the link,target,symbol,synthetic(Designware componenet) are used in FC tool?As per my understanding we can have .lib,.lef and TLU+ only.Can you clear my doubt please.

Thanks

Hi chethan,

Inputs for physical synthesis are RTL code, physical libraries (.lef), MMMC (.lib, sdc, RC coefficient or tlu+), floorplan def. These files are must need irrespective of tools. Note: TLU+ (synopsis terminology) and RC Co-efficient (cadence terminology) file both are same.

Hi

Thank you very much fyi.

floorplan def is needed as input to physical synthesis , how this file available before doing floorplan right! because it genrate after doing floorplan . so how can it will be given to input of physical synthesis?

So, to perform Physical aware synthesis. First we have to perform logic synthesis and need to provide gate level netlist to PG team. With the provided data, they do Floorplan and generates def file. So, from 2nd iteration, we will perform Physical synthesis with the def file provided by the PD team.

thanks! it’s really help.

I truly appreciate your feedback! It’s wonderful to hear that the content is making a positive impact—thank you for being part of this journey!

In synthesis will timing is not met means what are the techniques wil use ? and synthesis will get DRV’s ? if get means how to do.

please can u elaborate

In synthesis, major timing violations we get due to more logic in data path or SDC constraints (missing constraints, strict or loose values of constraints). So, by updating these constraints timing will get clear, but doing this is not that easy that’s why we say synthesis is the iterative process. Updating constraints and checking the timing, this is a loop until design timing get clean.

Thank you very much for clear explaining.

Thank you for your positive response. We are always here to help our followers…

But i heard in synthesis also will do group paths is it right. if right in which stage we do

Yes, group path also there in synthesis. If you want to optimize a specific cost group to meet target slack.

physical syntheses same as pnr or not

Physical synthesis is conversion of RTL code to gatelevel netlist and also placement. But estimated placement can be done. Coming to PnR tool performs actual placement.

Hi,

thanks for the information. very much helpful.

in which stage tool inferred transparent latch, But instead of latch their should be a flop. how will know and which command we use?

can you share this answer

Tool inserts initial mapping stage only

Hi

How the MBIT ratio will vary during synthesis and how to increase the ratio.

How the ICGs will come into the picture during the synthesis.

May i know pls.

Thanks

Hello,

Apart form vt swapping, drive strength is there any other way to reduce timing violations.?

Yes, there are way. First we need to identify why the timing issues are causing like in my recent project I faced timing issues because of bad floor planning (From PD team). So, we have to check DEF file. Group pathing also another way to fix timing violations.

Thank you

Can you explain about what is meant by target library & link library?Which library we will use in our design & why?

Target library

Also known as the destination library, this library contains the cells that are used to synthesize the design. The pointer variable target_library is used to specify the target library.

Link library

This library contains the libraries that are used to reference macros and other cells that are not synthesized by the design compiler. The pointer variable link_library is used to specify the link library. The link library describes the function of mapped cells before optimization.

In general, the target and link libraries are set to the same technology library.

Both libraries can be used in designs…

Can you please explain about integrated clock gating concept

We will upload ASAP.

Thank you

Is upsizing and downsizing is based on the width sizing can you elaborate?

And please give an overall view on widthing (width sizing)

Let’s say 1X inverter width is 1 unit length and 2X inverter width is 2 units of length. Here, why width is increasing means internally the count of transistors will increase compared to 1X vs 2X inverters. So, rising count of transistors need more area. So, width of the standard cell will increase. This will increase the capability of driving the more load (Fanout). I hope you understood.

We will upload topic on sizing.

Thank you

We can see that if we increase effort levels to optimize timing , we can see increase in inverters and buffers(cell count). During logic synthesis we use zeroWLM. So how does the tool place these cells?

Hi siddartha, if we are using zeroWLM in logic synthesis, we only see cell delays. Based on the cell delays, tool calculates the timing of each path. If there is violation in the path, tool optimizes the path by inserting the inverters and buffers to control the fanout of each standard cell. And for zeroWLM, we take some margin of the clock and add it to the uncertainty. lets assume 25% of clock period allotted to the net delays. The tool have to use 75% of the clock for each timing path. Thats why we may see the timing violation on each path…

Difference between getch cells and wvgetch cells.

Hi sai, your question have 2 views. Like gtech cells there are 2 concepts.

1) Generic cells –> Generic technology cells are standard building blocks designed for general-purpose use, like basic functionalities such as logic gates, flip-flops, and other commonly used elements. They are designed to meet certain specifications and performance criteria for a broad range of applications.

2) Global cells –> global technology cells may incorporate advanced optimization strategies to achieve specific global design objectives, like these cells could be designed using advanced methodologies aimed at achieving global optimization goals such as minimizing power consumption, maximizing performance, or reducing chip area. They may involve techniques like floorplanning, placement, and routing optimization to ensure optimal overall chip design. Mainly it is for chip level optimization.

WVGtech cells: Weighted Voronoi Graph technology, it employed to represent and optimize various aspects of the layout, such as wire lengths, timing, power consumption, and area. WVGTECH cells primarily focus on local optimization within specific regions of the chip layout, aiming to improve the placement and routing of individual cells or small groups of cells.

Thank you

Why max fanout is treated as soft constraint and wt if max fanout effect our design? Please explain it a little depth for better understanding.

See, timing always depends on DRVs. There are 4 types of DRVs which are Capacitance, Transition, fanout and wire length. Here, we consider mainly Capacitance, Transition and fanout. In there 3 DRVs, fanout is soft constrain and Cap and tran are the hard constrain. Because, if fanout is more, capacitance will be more. If capacitance is more, transition will be more. This will impact the timing. But assume, capacitance and transition both are not violating this will not impact the timing even the fanout is violating. If cap, tran and fanout all are violating or any 1 DRV either cap nor tran along with fanout. Then we have to fix fanout.

I hope you understand

so if we see any unresolved references issues in the synthesis stage what we will do? how to resolve the issue

Unresolved references are occur because of missing cells information in libraries or missing some of RTL file. To resolve this, identify missing RTL files or provide proper libraries.

if there are any multidriven nets are there what are the reasons for that and how to resolve those issues?

Multidriven nets are created because of the RTL code. This can be fixed by changing RTL code.

Hi,

We Place the cells, perform optimization etc in Syn stage. Then why we need PnR?

At syn stage, we can say its an estimated placement and not actual placement. The results at synthesis stage will meet the placement stage results, like congestion, timing, power and area etc. So, simply we can say physical aware synthesis is about estimation of PnR.

Thanks

Hi,

In physical synthesis, we have to perform logical synthesis then take floorplan def (which will be based on synthesized netlist) as a input for physical synthesis. is my understanding proper?